阻抗匹配调试测试方法及参考建议

RF同轴线工程师在设计芯片和RF天线间的阻抗匹配时是否也遇到过这样的问题,根据数据手册的参数进行匹配设计,最后测试发现实际结果和手册的性能大相径庭,你是否考虑过为什么会出现这么大的差别?还有,匹配调试过程中不断的尝试不同的电容、电感,来回焊接元器件,这样的调试方法我们还能改善吗?

一、理想的匹配

通信系统的射频前端一般都需要阻抗匹配来确保系统有效的接收和发射,在工业物联网的无线通信系统中,国家对发射功率的大小有严格要求,如不高于+20dBm;若不能做到良好的匹配,就会影响系统的通信距离。

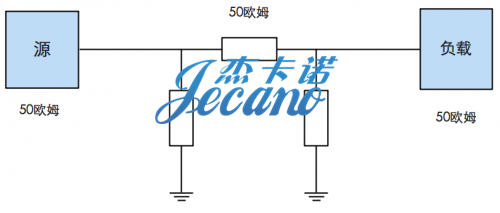

射频前端最理想的情况就是源端、传输线和负载端都是50Ω,如图1。但是这样的情况一般不存在。即使电路在设计过程中仿真通过,板厂制作过程中,线宽、传输线与地平面间隙和板厚都会存在误差,一般会预留焊盘调试使用。

图1理想的阻抗匹配

二、造成与芯片手册推荐电路偏差大的原因?

从事RF电路设计的工程师都有过这样的经验,做匹配电路时,根据数据手册给的S参数、电路拓扑结构、元器件的取值进行设计,最后得到的结果和手册上的差别很大。这是为什么呢?

其主要原因是对射频电路来说,“导线”不再是导线,而是具有特征阻抗(特性阻抗)。如图2所示,射频传输线看成由电阻、电容和电感构成的网络,此时需要用分布参数理论进行分析。

图2传输线模型

特征阻抗(特性阻抗)与信号线的线宽(w)、线厚(t)、介质层厚度(h)和介质常数()有关。其计算公式如下:

![]()

由公式可以知道,特征阻抗(特性阻抗)和介质层厚度成正比,可以理解为绝缘厚度越厚,信号穿过其和接地层形成回路所遇到的阻力越大,所以阻抗值越大;和介质常数、线宽和线厚成反比。

因为芯片的应用场景不同,虽然电路设计一样,但是设计的PCB受结构尺寸、器件种类、摆放位置等因素的影响,会导致板材、板厚、布线的不同,引起特征阻抗(特性阻抗)的变化。当我们还是沿用手册给的参数进行匹配时,并不能做到良好阻抗匹配,自然会出现实际测试的结果与手册给的结果偏差较大的情况。杰卡诺/JECANO——极细同轴线束领域的顶级生产厂家!VByOne|LVDS|eDP|Cable|VBYONE|KEL|屏线|连接线;为客户提供高效、优质、可靠的信号及电源传输解决方案!!!

虽然我们不能完全照搬芯片手册电路的所有参数,但可以参考其中的拓扑结构,如π型、T型或者L型等。那接下来我们应该如何调试那些参数呢?

三、常规的调试方法

完成PCB设计之后,进入调试过程,有的工程师对这个过程茫然失措,不知道该如何入手。有的工程师会回到数据手册,把手册提供的参数直接焊接到PCB上,通过频谱仪观察功率输出,若不符合期望值;则调整其中的电容和电感,改大或者调小,然后焊回到PCB上,不断的迭代,直到输出值符合期望。

这种方法由于无法得知PCB板上分布参数的阻抗,只能不停的焊接更换参数调试,导致效率很低,而且并不适合调试接收链路的阻抗匹配。

四、是否有更有效的调试方法?

如果我们能知道PCB板上分布参数的阻抗,就可以通过史密斯圆图进行有据可循的阻抗匹配,减少无谓的参数尝试。分布参数的阻抗有两种方法可以获得:第一,使用仿真软件建模仿真,但是建立模型需要知道材料、尺寸、结构等条件,其工作量不亚于直接调试;即使能建立模型,如何保证其准确性也值得考究。第二,使用网络分析仪直接测量,该方法直观而且结果准确。下面介绍如何通过网分直接得到特征阻抗(特性阻抗)。(杰卡诺/JECANO——VBYONE,KEL,VByOne,LVDS,eDP,Cable,屏线,线束,排线,连接线,同轴线,测试线,VBYONE屏线,KEL同轴线,VByOne屏线,LVDS屏线,eDP屏线,高清屏线,军工线束,汽车线束,医疗线束,工控屏线,设备屏线,游戏机屏线)

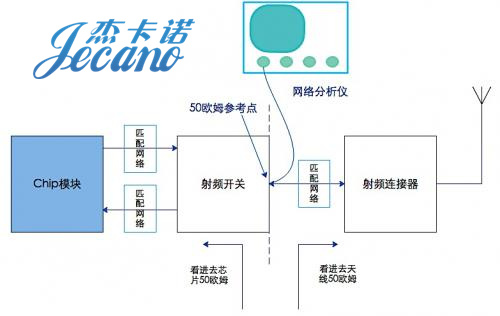

下图3是调试与匹配电路参考图,由芯片模块、射频开关和天线组成。把射频开关输出端作为50 Ω参考点,此处接入网络分析仪分别测量传输线到天线的阻抗和传输线到芯片端口的阻抗。通过匹配之后,希望从该点往天线方向看进去是50 Ω和往芯片方向看进去也是50 Ω。选择这里作为50 Ω参考点主要有两方面考虑:第一,该处到天线端是接收和发射的共同链路,只需要匹配一次,同时把天线对阻抗的影响也考虑了;到芯片端分别是接收和发射链路,需要分开匹配;第二,虽然匹配电路次数变多,但是每次匹配元器件数目少了,减少相互间影响,提高匹配效率。

图3调试与匹配参考图

五、测量分布参数阻抗

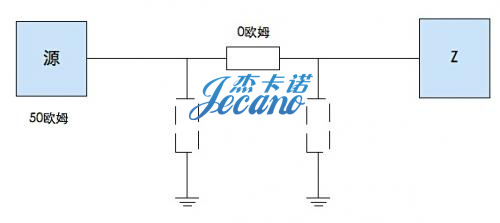

测量之前,将网络分析仪进行校准。首先把PCB板上除匹配网络的器件都焊上,然后把阻抗网络的落地元件断路,串联元件用0Ω电阻短路,如图4所示。尽量不使用焊锡短路,因为对高频电路来说,焊锡容易产生寄生效应,影响测量结果。

图4焊接调试器件

进行天线匹配调试期间,需要断开同芯片的连接。进行芯片匹配调试期间,需要断开同天线匹配组的连接,接收链路的匹配和发射链路的匹配通过开关切换分别进行调试。

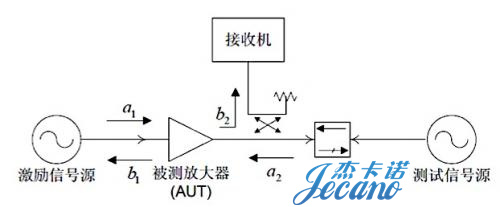

需要特别注意的是测量发射链路的阻抗,一般来说我们只要得到静态或者小信号发射的阻抗就能帮助我们完成设计,因为芯片发射时处于线性放大区,得到阻抗后只要微调器件,就能达到最佳的输出功率。如果需要更准确工作状态时的输出阻抗呢?当然也是可以的,这就需要我们加入更多的器件,如图5。

图5测量芯片发射时的S22

在图5中,被测放大器就是芯片的功率放大器,使其进入最大功率输出;而测试信号源则提供一个反向输入信号a2到放大器;放大器输出端所产生的反射信号b2 通过定向耦合器被接收机检测到;b2与a2之比即为放大器的大信号S22 参数。需要注意两点:第一,被测芯片和测试信号源之间需要加定向隔离器,防止大信号损坏信号源;第二,芯片输出频率和信号测试频率要异频。

具体的调试步骤如下:

1.校准网络分析仪,校准到连接到板上的射频线缆;

2.通过网络分析仪测量阻抗;

3.借助史密斯圆图进行阻抗匹配;

4.选择合适的电容和电感焊接到PCB上;

5.测量无线芯片的输出和输入是否满足要求。

在匹配过程中,选择元器件一般遵循以下几个原则:

1.落地电容值不要过大,电容越大,容抗则越小,信号容易流入GND。

2.电容、电感值不要过小,因为存在误差,容值、感值越小,误差影响越大,影响批次的稳定性。

3.电容、电感选择常规值,方便替换和备料采购。

阻抗匹配过程中,我们首先要理解数据手册的参数,找到指导电路设计的依据,如电路拓扑图、S参数等;在调试过程中,借助网络分析仪测量实际电路的阻抗,使用史密斯圆图辅助我们完成设计;最后对电容、电感的选择也给了参考建议。希望本文能给正在阻抗匹配中的你一些帮助。

杰卡诺/JECANO——极细同轴线束领域的顶级生产厂家!VByOne|LVDS|eDP|Cable|VBYONE|KEL|屏线|连接线;为客户提供高效、优质、可靠的信号及电源传输解决方案!!!

- 上一篇:典型的特征阻抗值 2019/9/4

- 下一篇:液晶屏LVDS上屏线“单8” “双8”的定义!屏线,线束,连 2012/5/21